As we have seen from discussions on chiplets and their routing standards in substrates, many of the routing techniques used in PCBs also apply in packaging. Microstrip and stripline structures can both be used in IC substrates, and the design approach is basically the same as in PCBs.

This routing is fine for the majority of digital interfaces, but when we get to wideband channels used in packaging targeting the fastest data rates, a different routing structure may be needed. To be more specific, the structure is a waveguide structure and is known as skip-layer routing.

This type of routing can be used in packaging and is essentially a waveguide structure for differential pairs. By taking a waveguide approach for differential pair routing, a designer can form wideband channels that can support the fastest interfaces being developed today.

This would include 224G-PAM-4 interfaces requiring 56 GHz of channel bandwidth. Although originally proposed for use in packaging, this type of routing could also be used in PCBs supporting 224G data rates.

As we will see in this discussion, this type of structure is needed to support the high channel bandwidths required for the fastest per-lane data rates, both on PCBs and in package substrates.

While the main motivation is to maintain signal integrity within the required channel bandwidth, EMI is also a motivator for using a waveguide structure thanks to the structure’s shielding effectiveness.

SKIP-LAYER ROUTING STRUCTURE

Skip-layer routing involves a type of waveguide structure for differential pairs.

Essentially, you have differential striplines routed between two planes, and the striplines are fenced with vias. This forms a differential coaxial waveguide structure in a package, which is normally used to route to the ball-out on the bottom of the substrate.

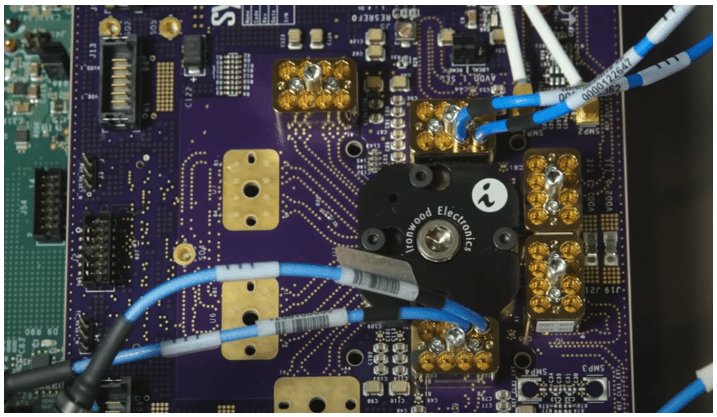

The image below shows a cross-section of this waveguide structure with some geometric parameters.

This type of routing, where a differential pair is routed near a plane with a via fence, is uncommon in PCBs. However, commercially available EDA software can certainly handle this structure.

For example, on a PCB, demonstration boards have been presented at industry events where the differential pair routing is done as striplines, forming a differential grounded coplanar waveguide on an internal layer.

Inside a package substrate, particularly packages with very high data rate channels, there will be multiple lanes being routed together to the ball-out on the bottom side of the package.

These lanes are running in parallel, with each lane requiring very high channel bandwidth, e.g., 56 GHz for 224G-PAM-4 interfaces. The differential pairs in each lane could be designed to run on the same layer or staggered on neighboring layers, such as the arrangement shown above.

Enjoying this article?

Subscribe to Interference Technology for expert coverage of EMI, EMC, and signal integrity challenges—plus immediate access to new digital magazine issues.

Subscribe here →

RESONANCES AND BANDWIDTH

Just from looking at the above cross-section, one would correctly assume that the waveguide structure provides many of the same benefits as a single-ended grounded coplanar waveguide structure typically found in RF PCBs.

In particular, the structure gives us some level of control over the following:

- Quasi-TEM cutoff frequency

- Cross-sectional area of each trace

- Differential crosstalk between adjacent lanes

- Shielding effectiveness of the via fence and thus edge-radiated EMI

Of these four factors, the most important factor determining the bandwidth of a skip-layer routing channel is the quasi-TEM cutoff frequency. This frequency is the highest frequency at which a wave or broadband signal can propagate in the quasi-TEM mode.

Above this frequency, a higher-order propagating mode or lossy mode could be excited, and propagation in these modes limits the signal power to a frequency range beyond the receiving interface’s available bandwidth.

Is there some way we can estimate what is the geometry of the waveguide region needed to ensure quasi-TEM propagation? As it turns out, there is a way to approximate just by looking at the rectangular eigenmodes of the cross-sectional geometry.

From electromagnetic waveguide theory, the next highest order mode will be at the minimum of the following two frequencies:

The minimum of these two possible values is an approximate bandwidth limit for the channel. Of course, this is only an approximation, the correct answer depends on the geometry of and spacing between the traces in the differential pair.

SHIELDING EFFECTIVENESS

The above discussion assumes that we have solid walls in the waveguide structure, but of course, the via fence in real skip-layer routing is not solid.

Here, the classic separation limit rules for vias determined in many studies on RF PCBs will come into play.

The typical center-to-center spacing limit on vias along the skip-layer route is given based on the bandwidth of the signal propagating in the waveguide:

![The variable "p" is less than either of the following two expressions:The constant c divided by the product of 16, π, f, and the square root of the product Dk; Or, alternatively, p is less than λ divided by 8. Mathematically, this is expressed as: p < (c) / [16π f √(Dk)], or p < (λ / 8)](https://interferencetechnology.com/wp-content/uploads/2025/04/Skip_Eq-2.png)

Here, f = 56 GHz for a 224G PAM-4 channel. The above result is often cited in EMC literature as a method for sizing via spacing in via fences.

One can reasonably expect that the via spacing equation above would hold for 56 GHz, which would require a center-to-center via spacing limit of approximately 0.37 mm, or 14 mils.

This is within the fabrication capabilities of the laser drilling and additive electroplating processes used in IC substrate fabrication.

There is an alternative result from studies on substrate integrated waveguides [1], which are very similar structures designed to elicit rectangular waveguide modes with the same approximate boundary conditions we find in skip-layer routing.

This result states that the via diameter should be between approximately 50% to 80% of the via pitch, which yields similar spacing values as the 1/8th wavelength result above.

The original 3D simulation study found that the result was valid into the ~30 GHz range, which would certainly support 112G PAM-4 signaling. The via spacing is needed to approximate a closed rectangular cavity around the differential pairs.

However, it will still determine leakage at high frequencies and thus the amount of channel-to-channel crosstalk. In general, tighter via spacing produces higher shielding effectiveness at higher frequencies.

Unfortunately, we eventually run into manufacturing limitations, which would prevent pushing available channel bandwidths even further to accommodate the next data rate doubling to 448G.

GETTING TO 448G PER LANE

At 224G with PAM-4 modulation, standard BGA packages with 1 mm pitch maximum can accommodate the bandwidth requirement for these channels [2].

At the next data rate doubling, there will be several challenges to accommodate the new data rates depending on the modulation format being used and the channel bandwidth requirements. These include:

- Via-to-via spacing in skip-layer routing

- Dielectric constant of the package substrate material

- Substrate layer thickness

- Via transitions from skip-layer routing into the PCB

Current BGA packaging with standard pitches at 0.8 mm or smaller can already handle higher bandwidths, and simulation data showing this can be seen in the references.

This should not be surprising as RFICs can already operate above 56 GHz bandwidths, but those RFICs are not relying on wideband signaling.

Pushing wideband signaling above 56 GHz with low group dispersion and no higher-order mode excitation may become a manufacturing challenge as well as a design and simulation challenge.

It remains to be seen what the next modulation format will be under the IEEE 802.3 standards, but this could determine whether current package substrate technologies can support the next data rate doubling or whether new approaches will be needed.

REFERENCES

[1] Kordiboroujeni, Zamzam, and Jens Bornemann. “New wideband transition from microstrip line to substrate integrated waveguide.” IEEE Transactions on Microwave Theory and Techniques 62, no. 12 (2014): 2983-2989.

[2] Intel. 224G Package and PCB Investigations and COM Reference. P802.3df Working Group.