In the world of signal integrity, we rely on many important metrics to qualify high-speed channel designs, both before prototyping and during prototype testing.

There is a common group of signal integrity metrics that appear in high-speed digital interface standards and which need to be implemented in printed circuit boards and packages.

These signal integrity metrics have helped guide the way from Gbps interfaces all the way up to the fastest interface implementations we see today, running at 224G PAM-4 per lane.

This article will give readers an overview of these important signal integrity metrics, each of which may be examined at the interconnect level or the system level.

LIST OF SIGNAL INTEGRITY METRICS

Although interfaces with faster data rates are clearly more advanced in terms of their function and evaluation, they rely on the same set of signal integrity metrics as used long ago, before Gbps interfaces became common.

What has become more advanced is the analysis and interpretation of the results, as well as the resulting changes to PCB or package layouts in order to improve signal integrity.

Whether looking at low speed interfaces at ~1 Gbps NRZ or ultra-fast interfaces at 224G PAM-4, we are often trying to answer the following questions when examining signal integrity:

- Does the channel provide the minimum required quasi-TEM bandwidth?

- Is there excessive loss (absorption or reflection) during propagation?

- Is crosstalk from nearby interconnects within acceptable limits?

- Do losses, crosstalk, and bandwidth limiting create excess bit errors?

S-parameters

The workhorse of signal integrity measurements and analysis is S-parameters, which collectively define transmission and loss of signal between the input and output ports of an interconnect.

There are multiple ways to use or formulate S-parameters in order to quantify other important signal integrity metrics. Thus, most signal integrity metrics will reference S-parameters when looking in the frequency domain.

Depending on the number of ports in your system and what the S-parameters are meant to represent physically, we can have several different definitions for signal integrity metrics.

The table below provides port numbering and some metrics which are qualified with these S-parameter definitions specifically for transmission lines.

Note that Table 1 addresses transmission lines, but technically the S-parameter definitions for any DUT (either single-ended or differential) would follow the exact same table.

At its root, the S-parameters quantify the input impedance of an interconnect between two terminated ports; this is then related to the characteristic impedance of the DUT or the coupling impedance between two coupled DUTs, e.g., coupling impedance that determines crosstalk.

Once an impedance is known, the propagation constant (and thus losses) is known. From there all other signal integrity metrics can be simulated

or calculated by hand.

Crosstalk and mode conversion are two sets of signal integrity metrics for differential interconnects; aside from the newest versions of DDR, many high-speed interfaces are differential, including 112G/224G SerDes lanes.

Crosstalk has always been a signal integrity metric at lower frequencies and is normally qualified by comparing the relevant S-parameter spectrum against an S-parameter mask.

Time Domain Reflectometry

Because impedance is the core signal integrity metric that influences all other metrics, we have a simple method to measure impedance by looking at reflection against a reference value.

This is where time-domain reflectometry (TDR) is used as it overcomes an important drawback of S-parameter measurements, most notably S11.

[table id=1 /]

In S11 (reflection) measurements, a VNA provides a frequency domain view of reflection due to an impedance mismatch, but it does not say where the major mismatch is which will lead to reflection.

This is overcome with a TDR measurement, which will show where the impedance mismatch is located along an interconnect, as well as whether there is excess capacitance or excess inductance.

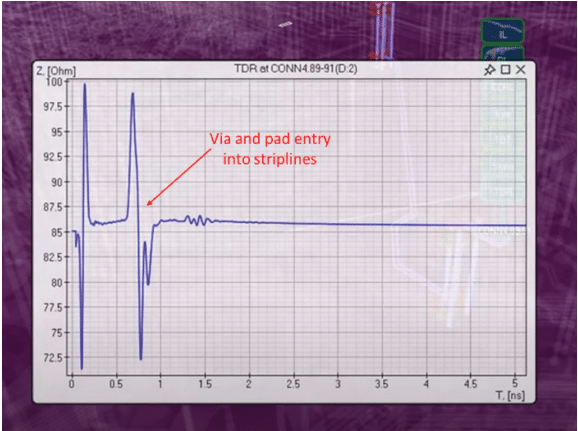

An example from Simbeor is shown in Figure 1.

Here the peaks in a TDR trace can be used to identify specific points along the length of the interconnect based on the corresponding propagation time; the peaks correspond to impedance discontinuities, which may illustrate excess parasitic capacitance or excess inductance.

Here we have a TDR spectrum for a PCIe lane routed as striplines, which shows the effects of the pad and via arrangement right at the input of the interconnect.

Do these peaks really matter? If they are noticed within your required channel bandwidth in the S-parameter spectrum, then the answer is “yes” and these features would need to be redesigned.

Physically smaller discontinuities along interconnects become more noticeable as the required channel bandwidth increases, i.e., as the data rate increases. This occurs because physically smaller deviations create noticeable reflections only at higher frequencies.

This means very small PCB or package features like pads/antipads and vias will create reflections that become noticeable in 224G PAM-4 interconnects, which require at least 56 GHz of bandwidth.

These very specific features can be identified in a TDR plot and selected for design modification if they create excess reflection.

A related test that is performed in simulation is the impulse response of an interconnect; when the impulse response for an isolated transmission line is simulated, it is equivalent to a TDR simulation.

The goal is to qualify a linear network model for your interconnect or DUT in terms of causality, loss, and reflection leading to intersymbol interference.

Eye Diagrams

The last mile in qualification of a channel design is to generate an eye diagram. This is the closest representation you will get to real operation before you take measurements of your system.

An eye diagram is a simulation where a pseudorandom bitstream is used to examine the bit error rate (BER), a summative metric that allows one to determine whether cumulative signal integrity problems will cause a channel to exhibit unacceptably high data errors.

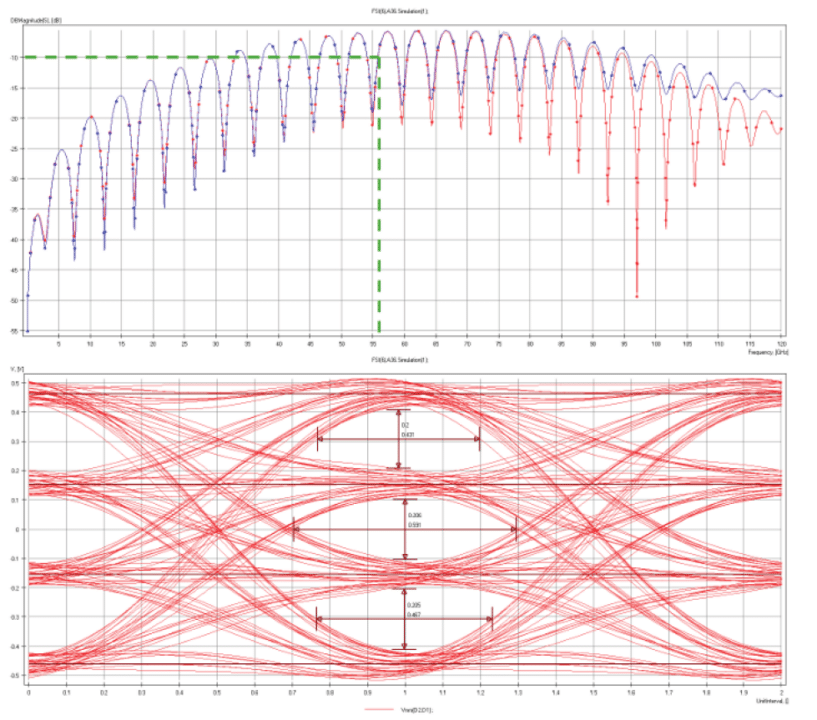

An example is shown in Simbeor above (Figure 2). In this image, any bit errors are determined by comparing with an eye diagram mask, or through automatic calculation.

The corresponding S11 spectrum for this differential interconnect illustrates a spot check limit at -10 dB which would be the maximum acceptable return loss.

As can be seen, the S11 plot rises above -10 dB before the channel bandwidth requirement of 56 GHz is reached, indicating there is excess impedance mismatch that will impact channel compliance.

In PAM-4 channels, the difficulty increases due to losses extending to higher bandwidths, reduced distance between signal levels, and greatly reduced skew budgets, all of which contribute to eye closure.

In these channels where high losses and excess jitter can cause eye closure, equalization or pre-emphasis might be used to bolster signal strength and recover the signal from the noisy bitstream.

These measures can be further examined in the eye diagram to ensure the incoming data can be resolved by a receiver.

Although the world is potentially reaching the end of wideband copper interconnects as we near the 56 GHz channel bandwidth requirement, the above metrics will continue to be the yardsticks against which we measure signal integrity.

Whatever trick is exploited to get to the next doubling of data rates, these metrics will continue to be used to qualify signal integrity in these more advanced channels.