Designers looking to build more advanced systems operating at higher data rates and bandwidths tend to rely on materials with low dielectric constant values, i.e., low-Dk materials.

It has gotten to the point where every high-speed PCB design guide implies that high-speed and RF designs will not function without a low-Dk material like Rogers or Arlon.

The reality is that the use of a low-Dk material in a PCB, or in more advanced substrate and package designs, is an engineering decision just like any other.

In PCBs, low-Dk materials provide benefits in terms of manufacturability, particularly in HDI designs, and the material selection is not always related to the electrical functionality of a product.

In packaging, the common materials used for substrate buildup tend to have lower Dk than organic PCB materials, but this extends channel bandwidths for certain high-speed interfaces.

Low-Dk materials come in a range of options and commercial products, and this article will outline the main factors driving the usage of a lower Dk laminate.

As we will see, you don’t always need a high-performance PTFE laminate, but there are times where the additional laminate cost can be a lifesaver for signal integrity and could reduce the overall cost of the product.

Why Everyone Thinks They Need Low-Dk PCB Materials

There are two very common reasons why basic design guides will recommend low-Dk PCB materials. These two common reasons have to do with signal integrity:

- Justification #1: Lower Dk laminates have faster signal propagation speed, thus it increases the critical length beyond which transmission line impedance calculations

are needed. - Justification #2: Lower Dk laminates create lower losses that are desirable in advanced systems.

The first statement is correct from a physics standpoint: signals traveling in lower Dk materials do have faster propagation speeds, and that would increase the critical length.

It is also true that commercially available lower Dk PCB laminates tend to have lower loss tangent, but this only affects dielectric loss, and the reverse of this statement is not universally true.

These are not the best justifications for using low Dk materials from a signal integrity perspective.

Lower Propagation Speed Does Not Matter

First, let’s address point number one. If you are building a system that is deemed “advanced,” then you should not look for an excuse not to calculate impedances.

It is extremely simple to calculate transmission line characteristic impedance or differential impedance for differential interfaces. This is thanks to a wealth of simulation tools built into CAD programs and online calculators for determining impedance.

The difficulty of calculating impedance is, therefore, a non-issue. Furthermore, as I showed in a prior article, the value of a “critical length” is arbitrary and requires calculating the impedance to implement correctly.

High-Dk Laminates Can Also Have Low Loss

While it is true that lower Dk PCB materials tend to have low loss tangent, the reverse is not true for higher Dk materials. For example, consider a Rogers 3010 laminate, with Dk = 10.2 and Df = 0.0022 at 10 GHz.

Compared to basic FR4 with Dk = 4.4 and Df = 0.02 at 10 GHz, the FR4 laminate has 4x the dielectric loss as the Rogers 3010 laminate despite its lower Dk value. We can see this as follows:

- Rogers 3010 dielectric loss ∝ (10.2)×(0.0022) = 0.02244

- Basic FR4 dielectric loss ∝ (4.4)×(0.02) = 0.088

The factor 4 difference in dielectric loss is very clear. The real difference in total loss when Df values are very low (0.001 or less) comes from differences in conductor size and conductor roughness in a given stackup, it is not just about the laminate’s Dk and Df values.

This is because, at low Df values, the copper loss becomes dominant starting from 5 GHz and exceeding 50 GHz (depending on material constants).

This is especially the case in more advanced designs where layers are thinner, and thus the traces are thinner.

Real Reasons to Use Low-Dk Laminates

Manufacturability in Thin Laminates

The first reason to use thin laminates is for manufacturability reasons, particularly when manufacturing designs with impedance controlled buses.

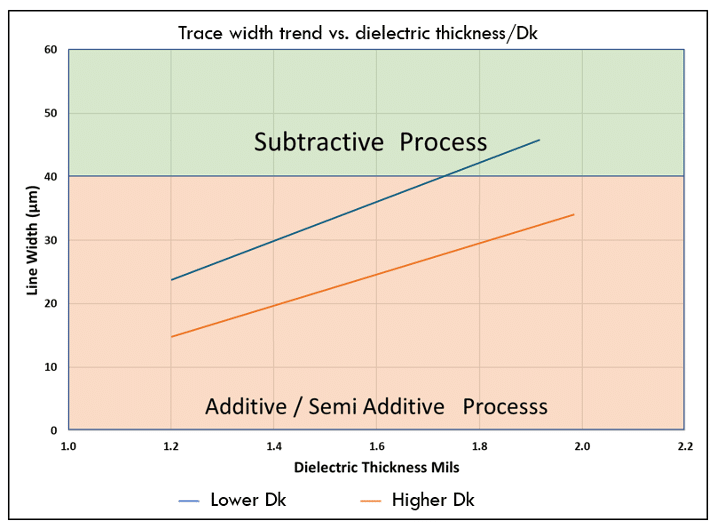

The requirement of fixed impedance on certain traces sets the trace width to a specific value, which is also a function of dielectric thickness and substrate Dk value.

If the laminate is too thin and the resulting trace width is too thin, the copper etching process will become more expensive. Eventually, at very small linewidths, the processing requirement switches to additive.

Figure 1 summarizes the trend on thin laminates, and as we can see from the graph, it is possible to maintain fabrication in the subtractive regime, which carries lower costs.

Another reason to stay in the subtractive range is availability of fabrication capacity. Additive copper deposition on PCBs at scale is currently only available in China and Taiwan, which may be a non-starter for some military and aerospace products.

Staying in the subtractive range expands the number of available locations where fabrication capacity can be accessed, which will be inclusive of capacity in the US and Europe.

Reducing the Dominant Copper Loss

As was mentioned above, copper losses become dominant when Df values are sufficiently low. These losses are determined by the skin effect and the roughness of the copper foil used to fabricate the PCB.

For microstrips, the plating material used on the surface layers will also impact the copper losses as they can further roughen the copper or create magnetic losses (such as in platings with nickel seed layers).

Using a low-Dk laminate will require a larger conductor cross section in order to hit an impedance target, as shown in the above graph. This then reduces skin effect losses at high frequencies, which is very important in digital signals with bandwidths in the multi-GHz range.

Further reductions in conductor losses can be achieved by using alternative surface platings, using smoother copper foils, and preferring microstrip routing where possible.

Reduced Crosstalk and Mode Conversion

One consequence of the lower dielectric constant and the ability to use thinner dielectrics is more control over crosstalk.

When crosstalk occurs, it is mediated by ratio of mutual capacitance (Cm) between two traces to the self capacitance (Cs), and this capacitance ratio is dependent on the Dk value of the dielectric; the same idea applies to mutual and self inductances.

Using a lower Dk value provides smaller Cm/Cs ratio in the following ways:

- Fixed trace width, smaller laminate thickness: this allows Cs to be larger for a given trace width and spacing.

- Larger width → smaller trace spacing: When the width is made larger, a smaller crosstalk penalty would be seen when using a low Dk value compared to a high Dk value.

The first option gives a simple way to keep trace widths constant when swapping a laminate in the PCB stackup. The second option enables HDI design but with smaller crosstalk penalty compared to the case of a higher Dk laminate.

A related signal integrity issue in differential interfaces, which is also mediated by mutual capacitance and mutual inductance, is mode conversion.

In some ways, mode conversion in differential channels is a form of loss as it increases differential SNR values by converting some differential signal to common-mode signal, which is then canceled by the differential receiver.

For a given trace-to-trace spacing and width in a differential pair, a smaller Dk value will also decrease the mutual capacitance, which decreases mode conversion.

The Result: Increased Channel Bandwidth

In total, these effects surrounding low-Dk values serve to increase the TEM bandwidth of channels for digital signals.

Channel bandwidth becomes limited by losses and excitation of non-TEM propagation modes at sufficiently high frequencies. The effects on losses are outlined above and it should be very clear that low Dk manifests its benefits beyond a simple reduction in dielectric loss.

The other mechanism of increasing bandwidth is very important as the fastest digital interfaces start to extend their required channel bandwidths to 56 GHz, corresponding to 224G PAM-4 signaling.

This limit was previously reached in 112G NRZ channels, and further bandwidth extensions have only occurred by shifting from NRZ to PAM-4.

More advanced components and complex via structures in high density PCBs and packages can extend the bandwidths beyond 56 GHz by using higher density ballouts and low Dk materials in packaging and PCBs.