Introduction

The three top product failures I see constantly in my consulting practice are (1) radiated emissions, (2) radiated susceptibility, and (3) electrostatic discharge. After reviewing and testing hundreds of products over the years, I’ve come to the conclusion that products fail these tests for five common reasons (somewhat in order of incidence);

- PC Board Design—Poor layout and layer stack-up

- Cable Shield Termination and Pigtails—Cable shields are not terminated to enclosure or lack of common mode filtering for unshielded products, plus shield pigtails used

- Gaps in the Return Path—High frequency clocks or signals crossing gaps in the return path

- Power Distribution Design—Poor power distribution network (PDN) design

- Shielding Design—Apertures or slots in the shielded enclosure that are too long

1. PC BOARD DESIGN

The single most important factor in achieving EMC/EMI compliance revolves around the printed circuit board design. It’s important to note that not all information sources (books, magazine articles, or manufacturer’s application notes) are correct when it comes to designing PC boards for EMC compliance – especially sources older than 10 years, or so. In addition, many “rules of thumb” are based on specific designs, which may not apply to future or leveraged designs. Some rules of thumb were just plain lucky to have worked.

PC boards must be designed from a physics point of view and the most important consideration is that high frequency signals, clocks, and power distribution networks (PDNs) must be designed as transmission lines. This means that the signal or energy transferred is propagated as an electromagnetic wave. PDNs are a special case, as they must carry both DC current and be able to supply energy for switching transients with minimal simultaneous switching noise (SSN). The characteristic impedance of PDNs is designed with very low impedance (0.1 to 1.0 Ohms, typically). Signal traces, on the other hand, are usually designed with a characteristic impedance of 50 to 100 Ohms.

Understanding PC board design is all about two important concepts: (1) all currents flow in loops and (2) high frequency signals are propagated as electromagnetic waves in transmission lines. These two concepts are closely related and coupled to one another.

Currents Flow In Loops—Circuit theory suggests that current flows in loops from source to load and back to the source. In many cases of product failure, the return path has not been well defined and in some cases, the path is broken. The problem we circuit designers often miss is defining the return path of a high frequency signal back to the source. If you think about it, we don’t even draw these return paths on the schematic diagram – just showing it as a series of various “ground” symbols.

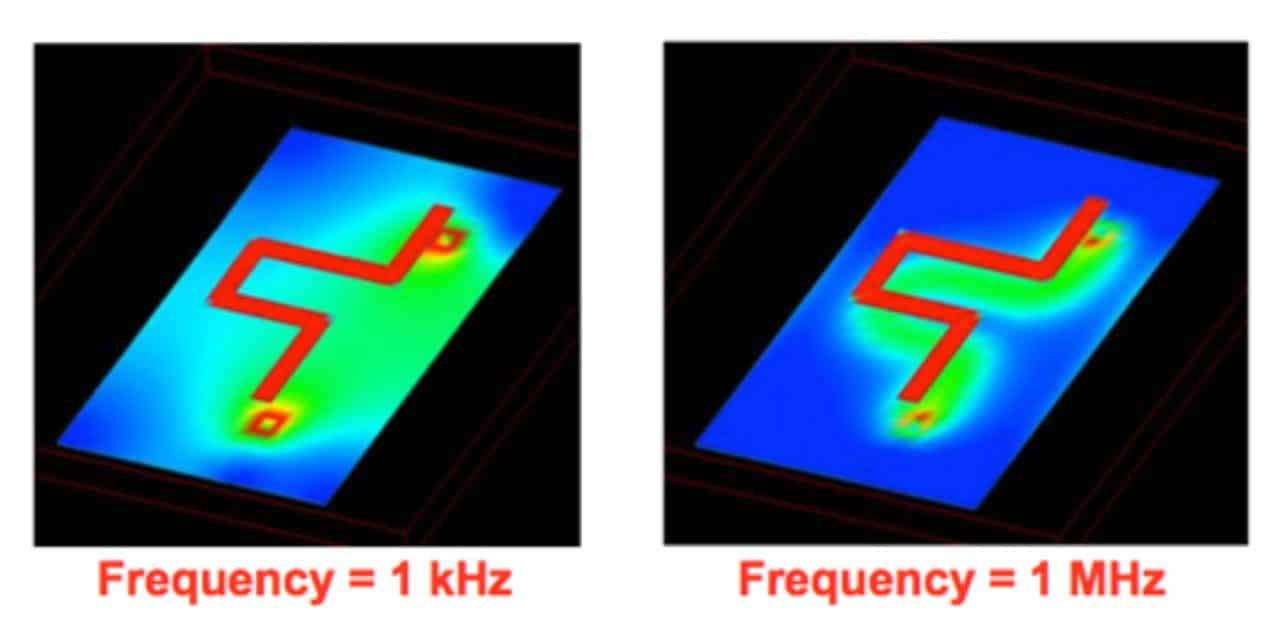

So what is “high frequency”? Basically, anything higher than 50 to 100 kHz. For frequencies less than this, the return current will tend to follow the shortest path back to the source (path of least resistance). For frequencies above this, the return current tends to follow directly under the signal trace and back to the source (path of least impedance). See Figure 1.

To reduce EMI, we need to minimize the area of these loops. Undefined return paths often result in large current loops from source to load and back to source. These large current loops start to look like loop antennas, coupling noise currents to “antenna-like” structures, such as cables, in your product or system.

Where some board designs go wrong is when high dV/dt return signals, such as those from low frequency DC-DC switch mode converters or high di/dt signals from digital logic and clock return signals get comingled with I/O circuit return currents, sensitive RF modules (especially receivers), or sensitive analog return currents. Just be aware of the importance of designing defined signal and power supply return paths. That’s why the use of solid return planes under high frequency signals and then segregating digital, power, and analog circuitry on your board is so important.

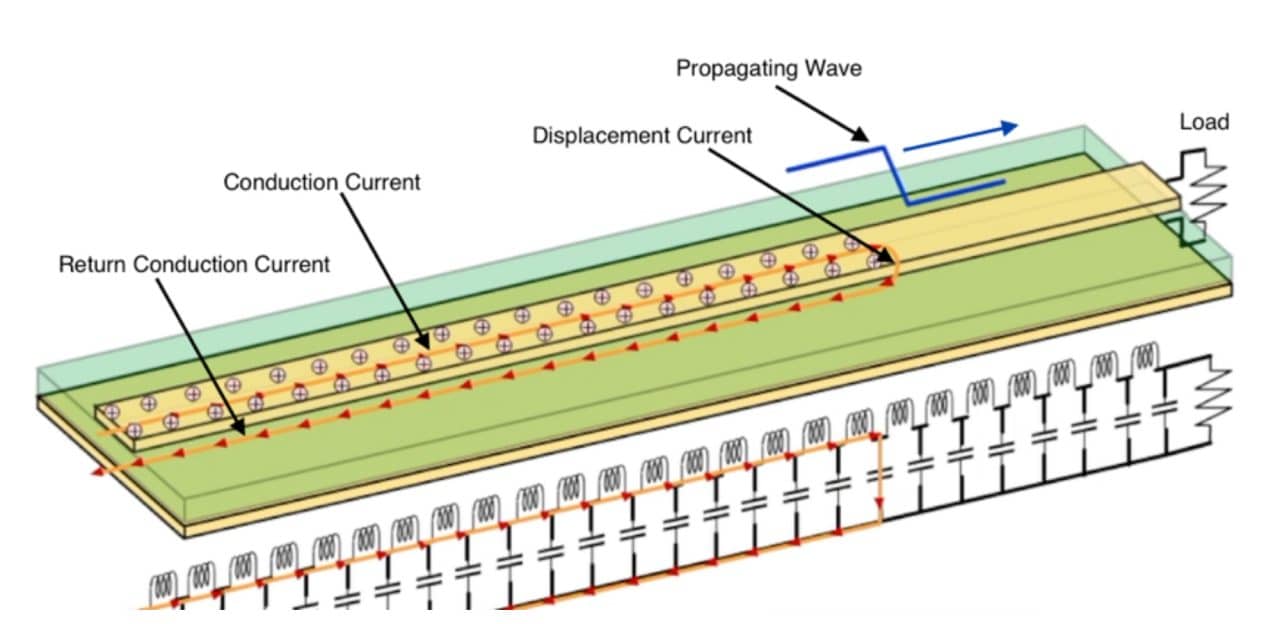

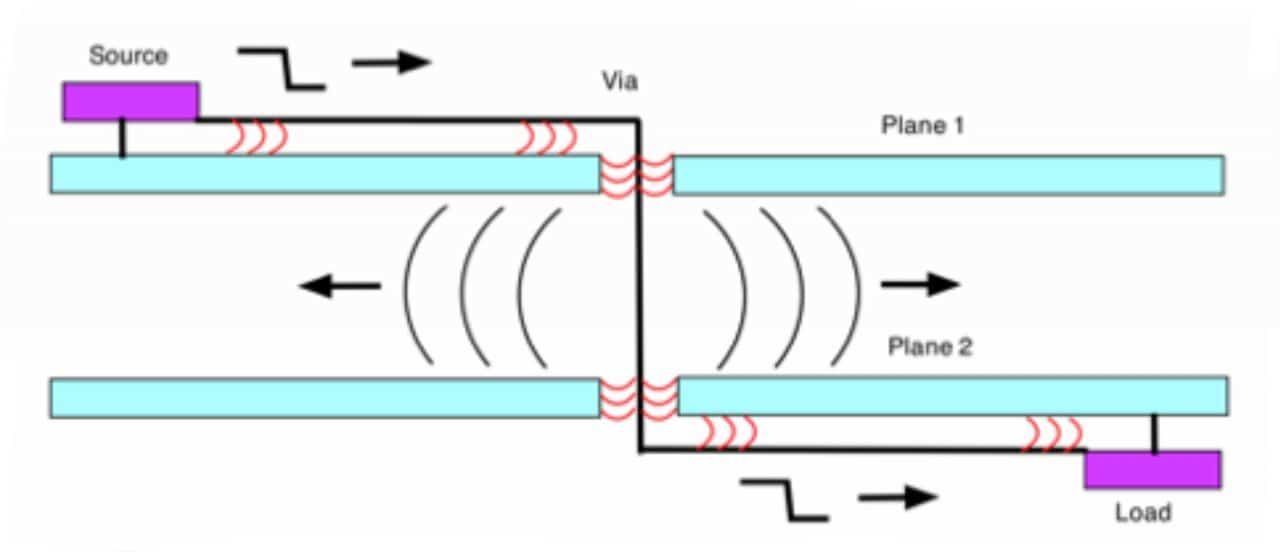

How Signals Move—At frequencies greater than about 50 to 100 kHz, digital signals start to propagate as electromagnetic waves in transmission lines. As shown in Figure 2, a high frequency signal propagates along a transmission line (circuit trace over return plane, for example), and the wave front induces a conduction current in the copper trace and back along the return plane. Of course, this conduction current cannot flow through the PC board dielectric, but the charge at the wave front repels a like charge on the return plane, which “appears” as if current is flowing. This is the same principle where capacitors appear to “pass” AC current, and Maxwell called this effect “displacement current”.

The signal’s wave front travels at some fraction of the speed of light, as determined by the dielectric constant of the material, while the conduction current is comprised of a high density of free electrons moving at about 1 cm/second. The actual physical mechanism of near light speed propagation is due to a “kink” in the E-field, which propagates along the molecules of copper. The important thing is that this combination of conduction and displacement current must have an uninterrupted path back to the source.

A high electric field is generated by high frequency digital signals occurring between the microstrip and return plane (or trace). If the return path is broken, the electric field will “latch on” to the next closest metal, which will not likely be the return path you want. When the return path is undefined, then the electromagnetic field will “leak” throughout the dielectric and cause common mode currents to flow all over the board. The uncontrolled field will also cause cross-coupling of clocks or other high speed signals to dozens of other circuit traces within that same dielectric through coupling to vias within the dielectric layer. The resulting common mode currents will tend to couple to “antenna-like structures”, such as I/O cables or slots/apertures in shielded enclosures, resulting in EMI.

Circuit Board Stack-Ups—Most of us were taught the “circuit theory” point of view and it is important when we visualize how return currents want to flow back to the source. However, we also need to consider the fact that the energy of the signal is not only the current flow, but an electromagnetic wave front moving through the dielectric, or a “field theory” point of view. Keeping these two concepts in mind just reinforces the importance of designing transmission lines (signal trace with return path directly adjacent), rather than just simple circuit trace routing. A successful PC board design accounts for both viewpoints.

In order to satisfy both the circuit and field theory viewpoints, we now see the importance of adjacent power and power return planes, as well as adjacent signal and signal return planes. Signal or power routed referenced to a single plane will always have a defined return path back to the source. Figure 3 shows how the electromagnetic field stays within the dielectric on both sides of the return plane. The dielectric is not shown for clarity.

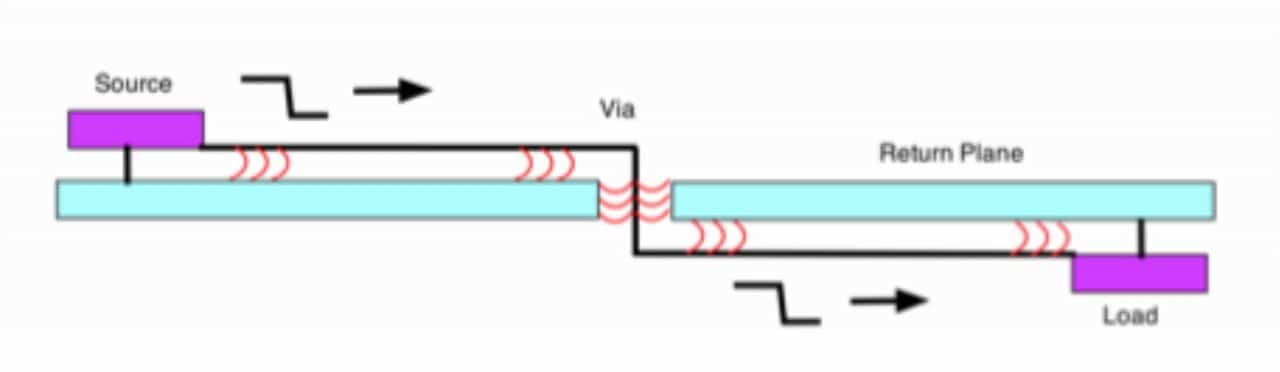

On the other hand, referring to Figure 4, if a signal passes through two reference planes, things get a lot trickier. If the two planes are the same potential (for example, both are return planes), then simple connecting vias may be added adjacent to the signal via. These will form a nice defined return path back to the source.

If the two planes are differing potentials (for example, power and return), then stitching capacitors must be placed adjacent to the signal via. Lack of a defined return path will cause the electromagnetic wave to propagate throughout the dielectric, causing cross coupling to other signal vias and leakage and radiation out the board edges as shown.

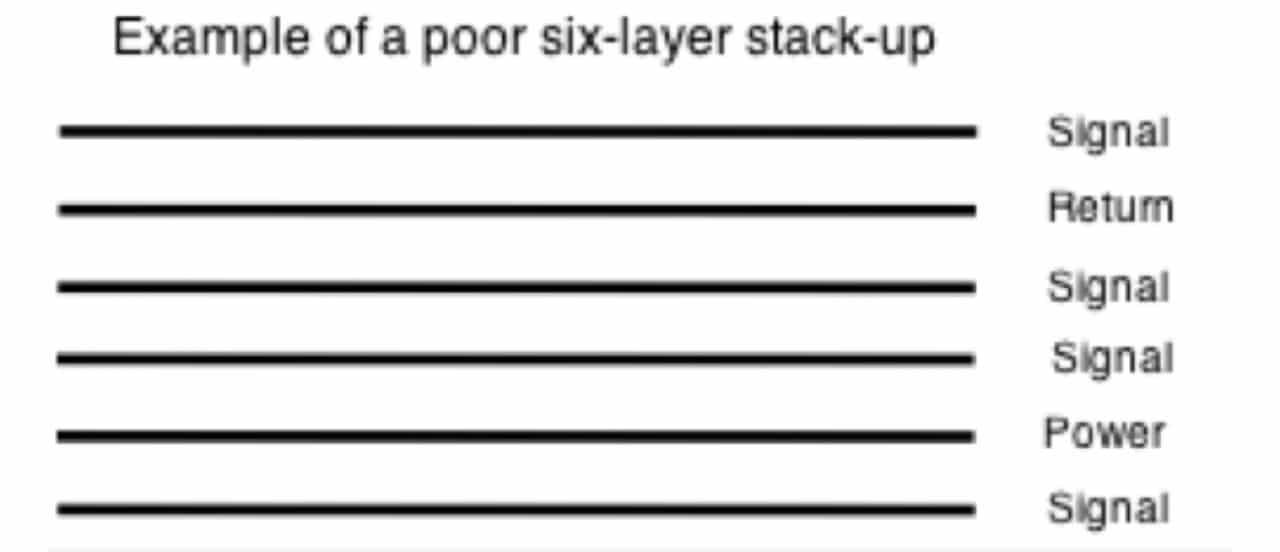

For example, let’s take a look at a poor (but very typical) board stack-up that I see often (Figure 5).

Notice the power and power return planes are three layers apart. Any PDN transients will tend to cross couple to the two signal layers in between. Similarly, few of the signal layers have an adjacent return plane, therefore, the propagating wave return path will jump all over to whatever is the closest metal on the way back to the source. Again, this will tend to couple clock noise throughout the board.

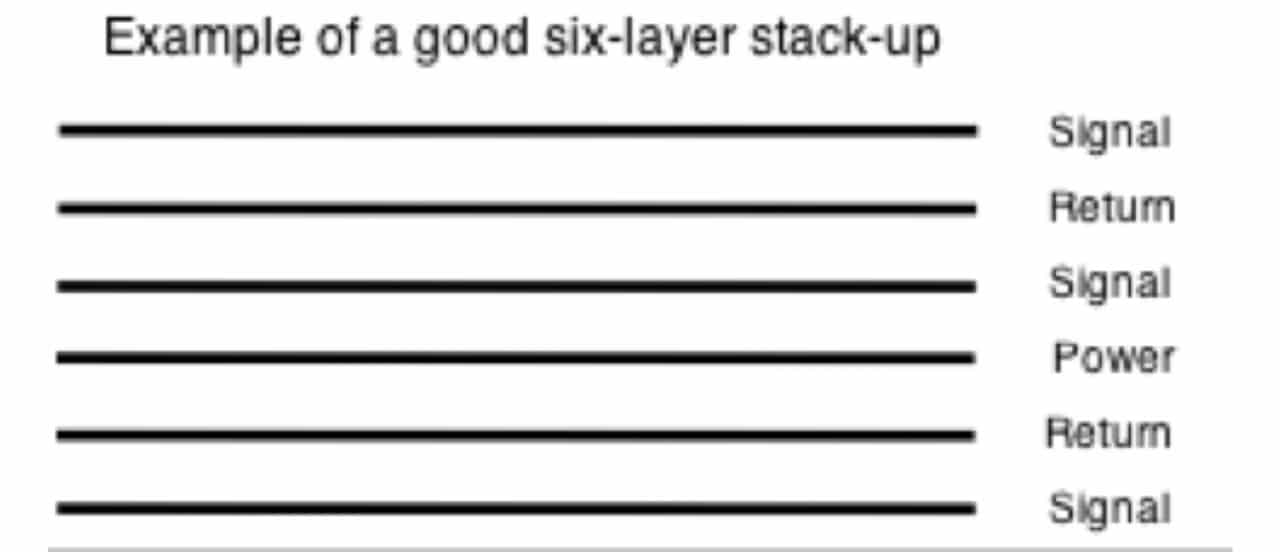

A better design is shown in Figure 6. Here, we lose one signal layer, but we see the power and power return planes are adjacent, while each signal layer has an adjacent signal (or power) return plane. It’s also a good idea to run multiple connecting vias between the two return planes in order to guarantee the lowest impedance path back to the source. The EMI performance will be significantly improved using this, or similar designs. In many cases, simply rearranging the stack-up is enough to pass emissions.

Note that when running signals between the top and bottom layers, you’ll need to include “stitching” vias between the return planes and stitching capacitors between the power and power return planes right at the point of signal penetration in order to minimize the return path. Ideally, these stitching vias should be located within 1 to 2 mm of each signal via.

Other Tips—Other design tips include placement of all power and I/O connectors along one edge of the board. This tends to reduce the high frequency voltage drop between connectors, thus minimizing cable radiation. Also, segregation of digital, analog, and RF circuits is a good idea, because this minimizes cross coupling between noisy and sensitive circuitry. Of course, high-speed clocks, or similar high-speed signals, should be run in as short and as direct a path as possible. These fast signals should not be run long board edges or pass near connectors.

Refer to References 1, 2, 3, and 4 for further details on PC board design and how fields move through transmission lines

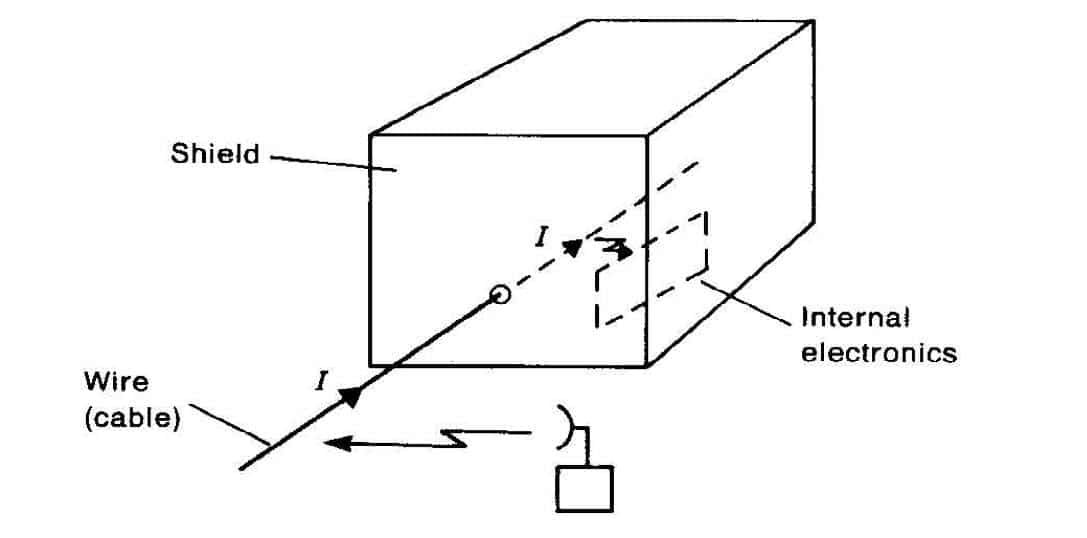

2. CABLE SHIELD TERMINATION

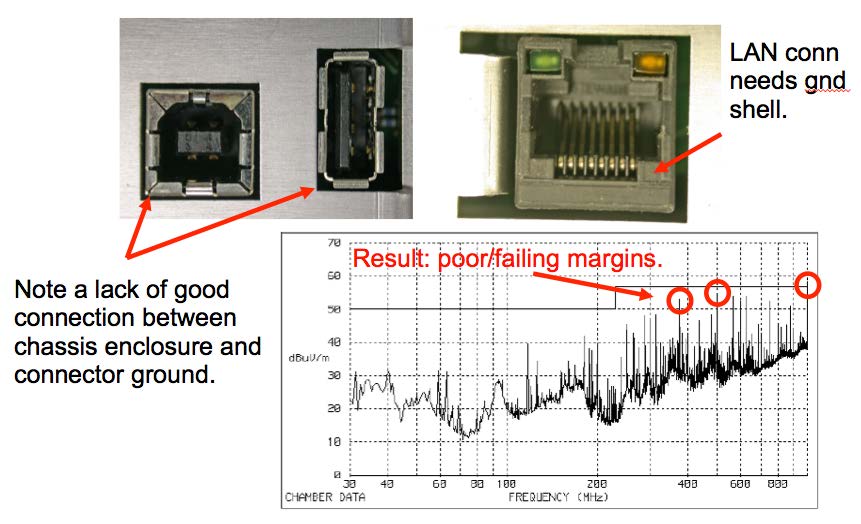

Cable Penetration—The number one issue I find when tracking down a radiated emissions problem is cable radiation. The reason cables radiate is that they penetrate a shielded enclosure without some sort of treatment – either bonding the cable shield to the metal enclosure or common mode filtering at the I/O or power connector (Figure 7 and 8). This occurs frequently, because most connectors are attached directly to the circuit board and are then poked through holes in the shield. Once the cable is plugged in, it is “penetrating the shield” and EMI is the usual result.

There are four combinations or cases that must be considered: shielded or unshielded products, and shielded or unshielded cables. Power cables are usually unshielded for consumer/commercial products and so require power line filtering at the point of penetration or at the connector of the circuit board. Shielded cables must have the shield bonded (ideally in a 360 degree connection) to the product’s shielded enclosure. If the product does not have a shielded enclosure, then filtering (usually common mode) must be added at the point of penetration or at the I/O connector of the PC board. Figure 8 shows the usual result when connectors simply poke through a shielded enclosure.

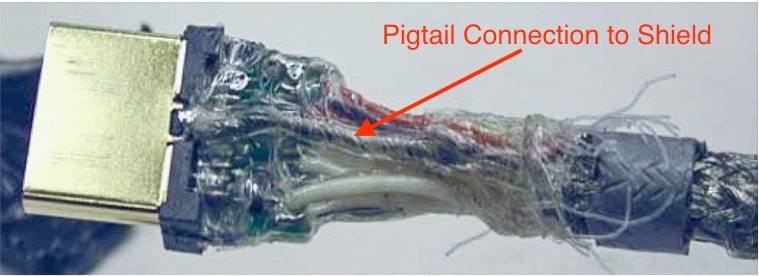

Cable Shield Terminations—Another potential issue is if the I/O cable uses a “pigtail” connection to the connector shell (Figure 9). Ideally, cable shields should be terminated in a 360-degree bond for lowest impedance. Pigtails degrade the cable shield effectiveness by introducing a relatively high impedance. For example, a 1-inch pigtail connection has 12 Ohms impedance at 100 MHz and gets worse the higher you go in frequency, thus defeating the cable shield.

This is especially problematic for HDMI cables, because the HDMI working group (http://www.hdmi.org) failed to specify the method for terminating the cable shield to the connector. Fortunately, they are aware of the issue and will better define a proper termination method in the next revision of the standard. In the meantime, there is no guaranty that a particular cable, when used for formal certification testing, will work well, or not. Trial and error of several brands is recommended.

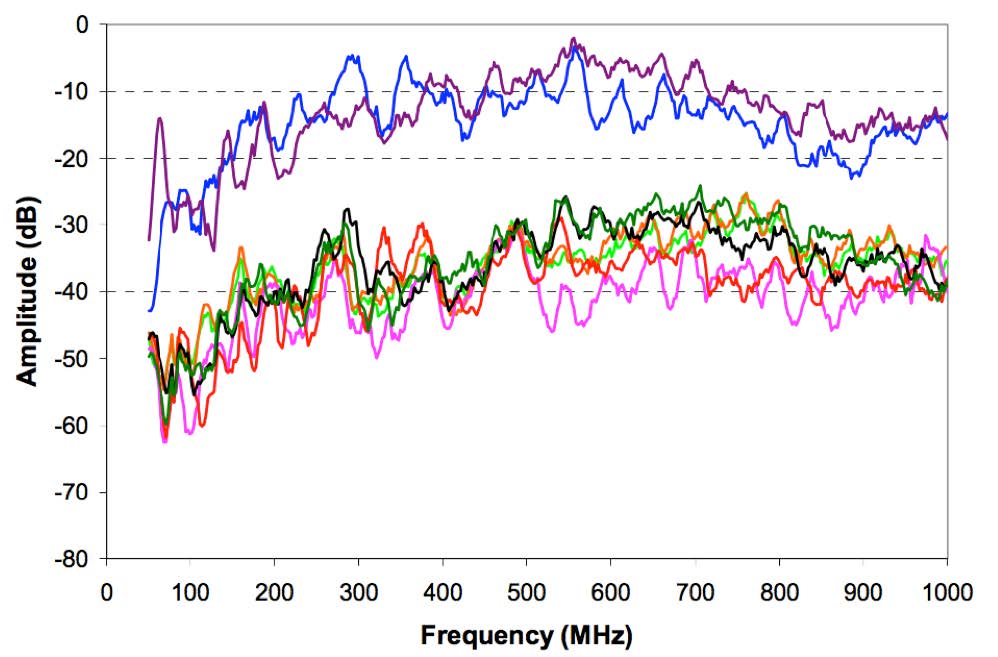

Here are the results in testing eight different brands of HDMI cable (Figure 10). Each was driven with a signal generator and measured in an EMI chamber while sweeping the frequency. For a detailed report of this test, refer to Reference 5.

3. GAPS IN THE RETURN PLANE

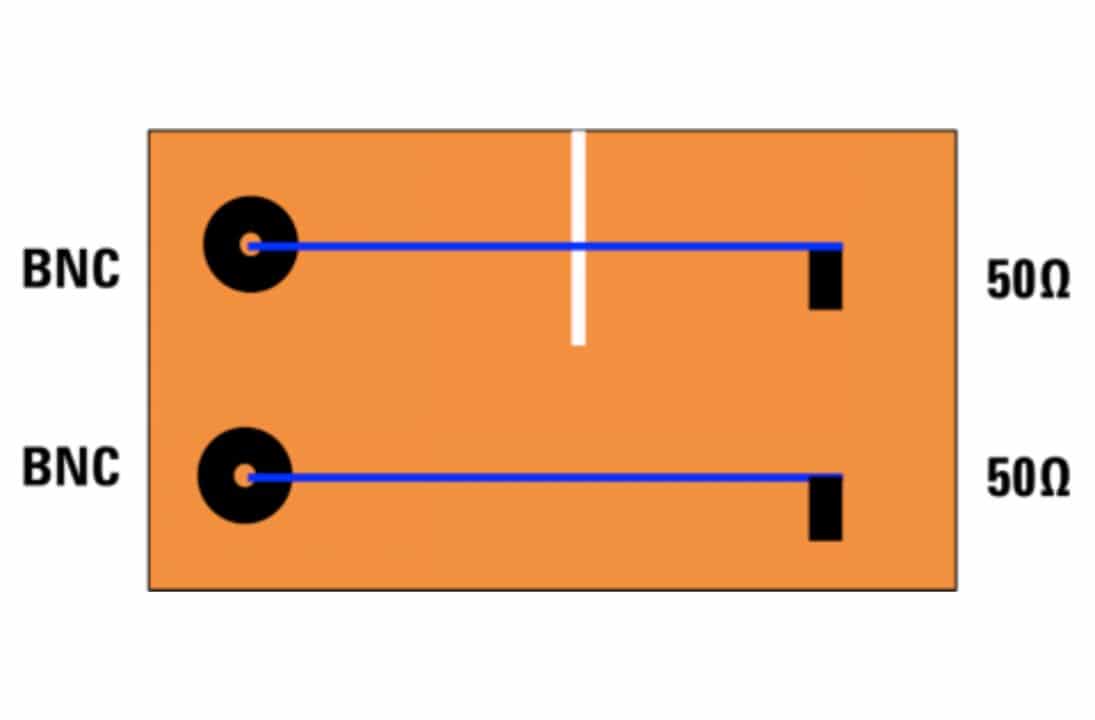

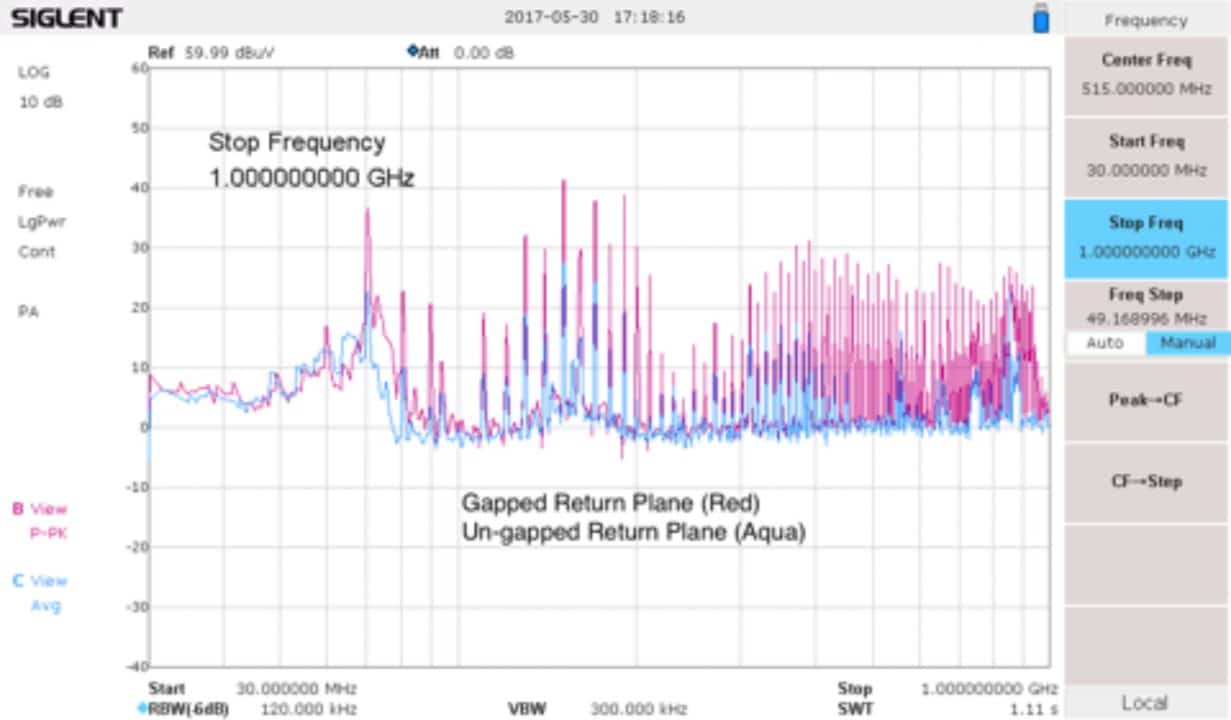

Breaks or gaps in the return path are major causes of radiated emissions, radiated susceptibility, and ESD failures. Let’s come back to the issue of a gap or slot in the return plane mentioned earlier and show an example of why it’s bad news for EMI. When the return path is interrupted, the conduction current is forced around the slot, or otherwise finds the nearest (lowest impedance) path back to the source. The electromagnetic field is forced out and the field will “leak” all over the board. I have an article and good demonstration video of this and how it affects common mode currents and ultimately, EMI. See Figure 11 and Reference 6. This would be a great demo to construct and show your own colleagues!

The difference between the gapped and un-gapped traces is shown in Figure 12. Note the harmonic currents are 10 to 15 dB higher for the gapped trace (in red). Failing to pay attention to the signal and power return paths is a major cause of radiated emissions failures.

4. POWER DISTRIBUTION NETWORK DESIGN

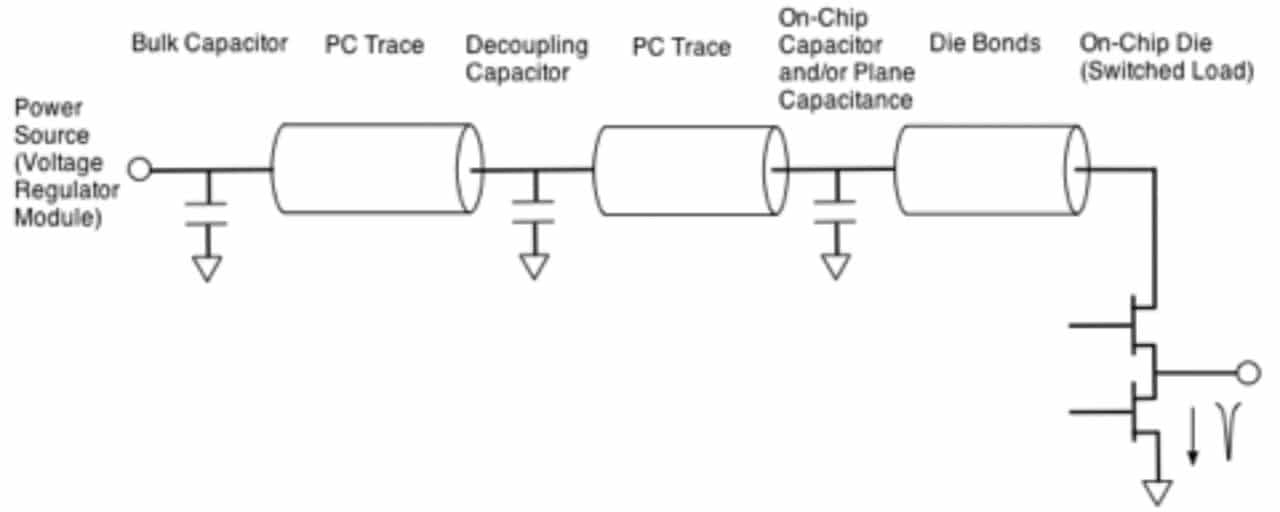

Power distribution network (PDN) design requires a low impedance (0.1 to 1.0 Ohms, typically) transmission line through at least 30 MHz. The purpose of a PDN is to transfer energy from the power source (often a voltage regulator module on the PC board) to the switching IC as fast as possible.

When the output stage of a digital IC switches from high to low or from low to high, there is a period of time when both output devices are partially turned on. This causes a large current pulse between the supply rail and power return pin of the IC. This “shoot through” current pulse tends to lower the supply voltage, causing what’s known as simultaneous switching noise (SSN) on the power rail. This SSN tends to propagate throughout the PC board. A well designed PDN minimizes this SSN.

Capacitors, in the form of bulk, decoupling, and board capacitance, are used to store enough energy to overcome the tendency of the power rail voltage to decrease. Figure 13 shows a typical circuit model of a PDN with the power source on the left, supplying energy to the IC on the right. In between, we have a series of energy storage capacitors and transmission lines (PC traces). Unfortunately, it takes significant time to transfer the required energy from the power source to the IC. It has been shown that it takes about 600 ps to transfer an amp of current across 1/16th inch of die bonds (Reference 10). That’s why it’s especially important to keep PDNs short and direct as possible.

Ideally, the total energy demand will be met by the “on-chip” capacitors, if any, plus the energy stored in the power plane capacitance. However, these are seldom enough storage, so we depend a lot on nearby decoupling capacitors to supply the remaining energy demand. It is critical for the decoupling capacitors to have as little series inductance (in the form of internal inductance and trace inductance) as possible. The greater this series inductance, the harder it is to supply the required energy to the load and SSN results with related noise coupling throughout the PC board.

Assuming the decoupling and any built-in capacitance of the PC board can supply the energy needs, then the job of the bulk capacitor is to “recharge” the energy of the downstream capacitors in between switching transients. For the fastest recharge times, the PDN must be in the form of low impedance transmission lines.

The bulk capacitors 4.7 to 10 μF, typ.) are usually placed near the power input connector and the decoupling capacitors (1 to 10 nF, typ) nearest the noisiest switching devices To achieve the lowest series inductance, all decoupling capacitors should be mounted as close to the IC to be decoupled as possible and right over (or close to) the connecting vias. Multiple vias should be used for each end of the capacitor to further reduce series inductance. More on PDN design may be found in References 7, 8, and 9.

5. SHIELDING DESIGN

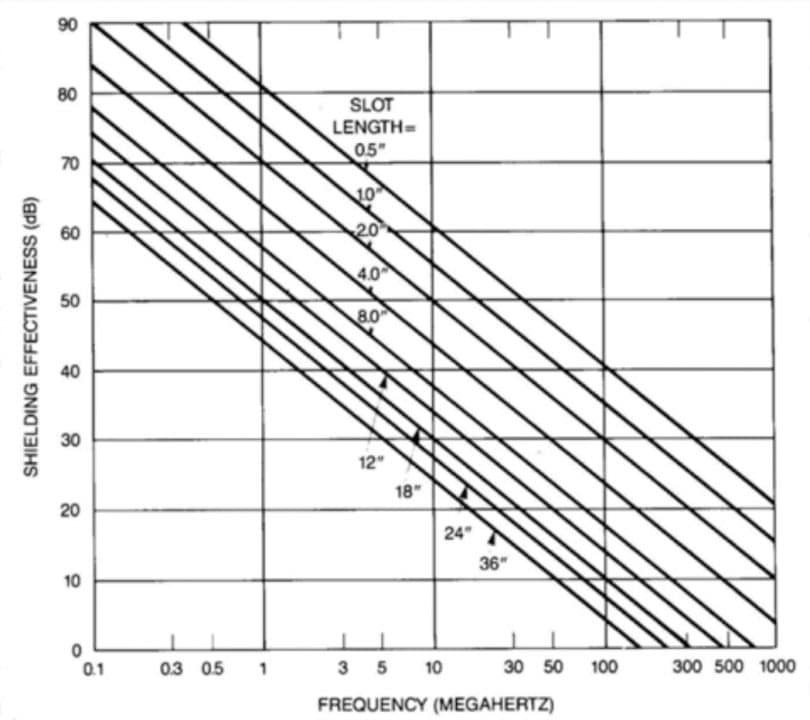

The two issues with shielded enclosures is getting all pieces well-bonded to each other and to allow power or I/O cable to penetrate it without causing leakage of common mode currents. Bonding between sheet metal may require EMI gaskets or other bonding techniques. Figure 14 shows a handy chart for determining the 20 dB attenuation of a given slot length. For example, if a product design requires at least a 20 dB shielding effectiveness, then the longest slot length can be just one-half inch.

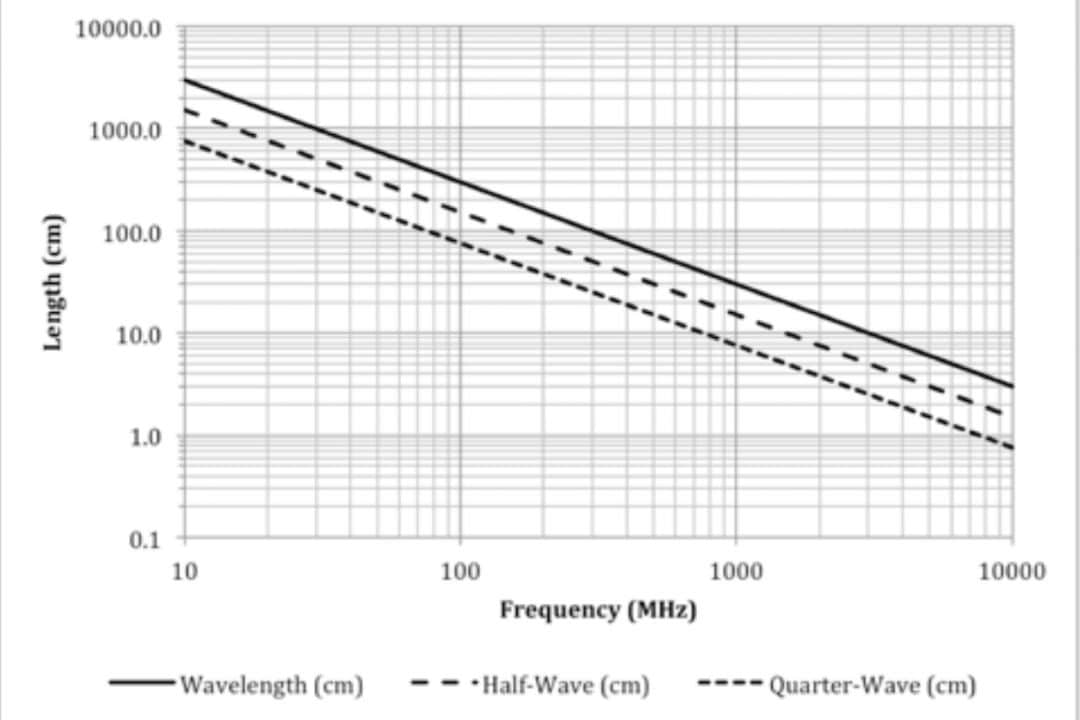

Slots or apertures in shielded enclosures become issues when the longest dimension approaches a half wavelength. Figure 15 is a chart of wavelength versus frequency. For example a 6-inch (15 cm) slot has a half wave resonance at 1000 MHz. Generally, ventilation holes should be patterns of round holes no more than 1/4-inch diameter. Patterns of slots may be used, but they should be no longer than 1/2-inch in order to preserve an adequate shielding effectiveness.

Reference 10 and 11 for more detail on shielding. Interference Technology also has a free downloadable 2016 EMI Shielding Guide with excellent information (Reference 12).

SUMMARY

Paying attention to these five product design faults will go a long way towards lowering the risk of EMI failure during formal compliance testing. Considering a proper EMC design early in project development will save tons of time and money in the end.

REFERENCES

- Bogatin, Signal Integrity – Simplified, Prentice-Hall, 2009.

- Morrison, Grounding and Shielding – Circuits and Interference, Wiley, 2016.

- Morrison, Digital Circuit Boards – Mach 1 GHz, Wiley, 2012.

Beeker, Effective PCB Design, https://www.nxp.com/files-static/ training_pdf/WBNR_PCBDESIGN.pdf

Bergey & Altland, EMI Shielding of Cable Assemblies, DesignCon 2008, http://www.magazines007.com/pdf/DC08_Dana_Bergey.pdf

Wyatt, Gaps in Return Planes – Bad News for EMI (with video demo), https://interferencetechnology.com/gaps-return-planes-bad-news-emi/

- Smith and Bogatin, Principles of Power Integrity for PDN Design, Prentice-Hall, 2017.

- Sandler, Power Integrity – Measuring, Optimizing, and Troubleshooting Power Related Parameters in Electronic Systems, McGraw Hill, 2014.

- Novak and Miller, Frequency-Domain Characterization of Power Distribution Networks, Artech House, 2007.

- Ott, Electromagnetic Compatibility Engineering, Wiley, 2009

- André and Wyatt, EMI Troubleshooting Cookbook for Product Designers, SciTech, 2014.

- Interference Technology’s 2016 EMI Shielding Guide, http://learn. interferencetechnology.com/2016-emi-shielding-guide/