Off-chip decoupling, or buffering, is a necessity.

Over the years, many papers and articles have been written about optimizing off -chip IC decoupling. Many IC vendor application recommendations feature a cluster of decoupling capacitors adjacent to the IC, in close proximity to one another—viz. an electrolytic capacitor along with a small and a large value ceramic capacitor at the various supply nodes. The basic conviction underlying this approach is that the decoupling impedance must be low over as broad a frequency range as possible.

In functional PCB design and IC applications, this approach holds true. However, when dealing with electromagnetic compatibility, an opposite track must be taken. In nearly all digital, as well as analog and RF designs, intentional on-chip decoupling capacitance is included—regardless of the origin of the IC design. When this on-chip decoupling exists in parallel with off-chip decoupling of lesser impedance, all interference currents will be forced off-chip rather than remaining confined within the tiny silicon chip area. An increase in the current loop area increases the amount of direct RF emissions from the IC package. Also, forcing the decoupling current to flow off-chip will cause ground bounce between the PCB reference plane and the silicon substrate. Specifically, Vss-net will become superimposed on all signal input and output lines connected to the IC and will cause all PCB traces to radiate as well.

A simple model will demonstrate the effect of the on-chip circuitry on the ultimate utility of the IC packages and PCB application. Typically, whatever occurs off – chip has little eff ect on on-chip circuitry at frequencies above 300 MHz, or even less. Essentially, when designed as a transmission line, the speed of charge transfer from off-chip to on-chip should not exceed the propagation delay of the package design—or even worse, exceed the LC time-constant of on-chip capacitance working in conjunction

with the package interconnect, lead frame, and bond wire.

ON-CHIP SOURCE REPRESENTATION

The on-chip interference source can be described as an AC or time-dependent current source in parallel to an on-chip capacitance (with some internal series resistance). In literature, this kind of noise source is often denoted by ICEM or LECC models representing the behavior of the core of a digital IC. For off -chip interfaces, the IBIS model is frequently used. In fact, version 4.1 and above are particularly well suited to the analysis of both signal and power integrity. For the purpose of EMC calculations, all AC or time-dependent currents through all the pins of the IC must be taken into account before a reasonable calculation of RF emissions can take place.

Achieving an effective AC or time-dependent current characterization requires factoring in every aspect of the entire application—including transistor level IC design, the 3D extracted parameters of the IC package, as well as all off -chip measures taken with regard to supply decoupling or signal loading. Alternatively, a limited suitable model can be defined.

When a load capacitance is measured at an output, and when that output signal transition is fast, then

the signal peak current will be as high as the voltage swing divided by the output driver impedance—i.e., Ron of the switching output since the load capacitance represents an instantaneous short-circuit impedance. When the same transition is applied to a transmission line as a load, the output signal peak current will be limited to the same Ron plus the characteristic impedance of that transmission line. With an Ron of 10 Ω and a Zo transmission line of 100 Ω, the output and the consequent peripheral supply current peak will be decimated. Th is assumption holds true as long as the transmission line length (i.e., its propagation delay) remains long in comparison to the rise time of the output signal.

The package, represented as an inductance or transmission line, and the off -chip decoupling capacitors are placed in parallel with the on-chip capacitance physically embedded within the on-chip interference current source. As long as the bypass impedance of the package impedance in series with the off-chip decoupling capacitors is low as compared to the on-chip decoupling impedance, all switching current will appear off-chip.

Simple CMOS chip designs have an equivalent on-chip capacitance of one nF and above. A typical acceptable figure might be 700 pF/mm2 (standard cell capacitance); whereas, in a best-case scenario tens of nF/mm2 (dedicated decoupling capacitance) might be achieved. In large processor designs— e.g., 100 mm2—on-chip capacitances of over 200 nF have been measured. The on-chip capacitance is the sum of the metal-to-metal power grid capacitance, the N well-to-substrate capacitances, and the gate oxide capacitances along with their interconnects as capacitive loads. Th is summed capacitance appears as soon as the nominal supply voltage is supplied to the IC and the CMOS transistors turn on. With normal CMOS IC designs, this on-chip capacitance can be measured as a function of the DC bias—i.e., supply voltage. More recent CMOS digital designs include embedded low drop out (LDO) voltage regulators or embedded IP-block enabling supply switches. With these recently designed chips, the total on-chip capacitance can only be estimated. Consequently, these newer digital designs should include on-chip decoupling underlying the regulators or switches since no off -chip remedies are available.

At low frequencies, the interference current will be distributed between the on-chip and off -chip capacitance in inverse proportion to their values. With 1 nF on-chip and 100 nF off -chip, 99 percent of the decoupling current will flow through the off-chip capacitance. At very high frequencies, the off-chip current will be blocked by the equivalent series inductance represented by the IC package.

SUPPLY BOUNCE

Safeguarding effective function and ensuring robust design of digital ICs necessitate on-chip voltage bounce that is equal, or less than, 10 percent of the nominal supply voltage. In the instance of nanometer CMOS designs, supply bounce values of 5 percent or less are recommended. In all these CMOS designs, a 10, or even 20, times larger decoupling capacitance embedded onchip is needed to compensate for the simultaneous switching capacitance onchip. Adhering to this design dictum, a total on-chip capacitance of 1 nF means that a maximum 100 pF of capacitances (gate–oxide + interconnect) should be allowed to switch simultaneously. Th is on-chip decoupling constraint applies only to the cycle-to-cycle operation of the digital CMOS design and does not hold true for an instantaneous change of its operating condition.

When the IC is supplied from an external supply voltage regulator module (VRM) or an external power management unit (PMU), the response rate of these regulators is typically around several μs for both the linear and switching regulator versions. For example, consider a digital CMOS IC running with a 1-GHz clock and going from an idle to an active state. In this instance, the long-term average supply current goes up from μA or mA to amps. Essentially, a thousand clock cycles have passed before the voltage regulator reacts appropriately. An off-chip decoupling or buffer capacitor is necessary to provide the amount of charge (Q = Δl·t = C·ΔV) needed to keep the supply voltage within limits during the response time of the regulator.

For example, when 1 amp is required over 1 μs, 1 μC of charge is required. When the nominal supply voltage is 1.8 V, the delta voltage allowed is 180 mV. The buff er capacitance value between the IC to be decoupled and the voltage regulator must be 6 μF, or slightly more, perhaps 8 μF. With a 5 percent supply voltage tolerance, the buffer capacitance must be twice this value.

In synchronous single-frequency digital CMOS designs, the peak current is typically three to 10 times higher than the average current. In this example, the supply currents reach a peak of three to ten amps. Th e supply current must diminish to zero before the next clock edge, and all activity ceases just before the next clock phase. Given these constraints, the peak current pulse width must be three to 10 times shorter than the period width. With a 1-GHz clock, the figure should be 100 to 330 ps.

RESONANCES

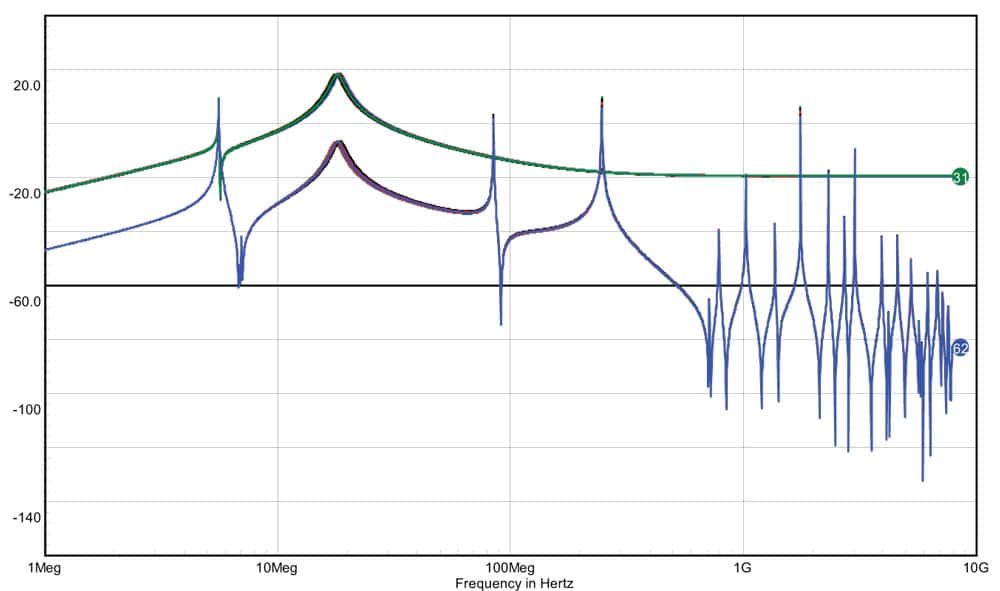

Resonances are often observed betweenoff-chip decoupling capacitances. In the case of electrolytic or small and large value ceramic devices, resonances also occur between the on-chip and off-chip capacitances. Clearly, the interference current produced by the IC will be multiplied by the quality of the resonant loop and will be radiated by the larger loop area and ground bounce voltage. Th e on-chip/off-chip resonance frequency is determined by the smallest capacitance value in that loop, typically the on-chip capacitance. This on-chip capacitance (with the total loop inductance) will determine the resonance frequency.

With a leaded QFP package, the lead length will be 4 mm, yielding an equivalent total inductance of 8 nH. That total along with an on-chip capacitance of 8 nF produces a resonance frequency of about 20 MHz. This particular supply system will not allow a supply recovery faster than 17 ns, the time for the fastest slew rate. When coupled (transmission) lines are used between the on-chip and off-chip decoupling position, the inductance will be decimated.

Still, 1.7 ns will be too long for a 1-GHz clock operation. Th e distance or lead length must be shortened or another decoupling technique should be employed—e.g., integrating decoupling capacitance in or on the package as is done with most PC processors. In all cases, resonances will occur between the various decoupling positions, and these resonances can be determined using simple analog circuit simulators such as SPICE.

When the activity within the IC does not coincide with a resonance of the supply decoupling circuitry, few problems will occur. Unfortunately, when it does coincide because of a (sub-) harmonic of the clock and/or data, interference may shoot sky high, and the functionality of the IC may be compromised. (Note: also the harmonic frequencies are of importance.) When such interference occurs within a particular data stream or data pattern, it can be difficult to arrive at accurate simulations or to detect the problem within actual applications.

The conventional wisdom for achieving a stable supply voltage is to place the capacitors in close proximity and to connect them to a PCB power plane structure of finite length with a proportionately lowered characteristic transmission line impedance. Support for this approach can be found in many sectors of the industry.

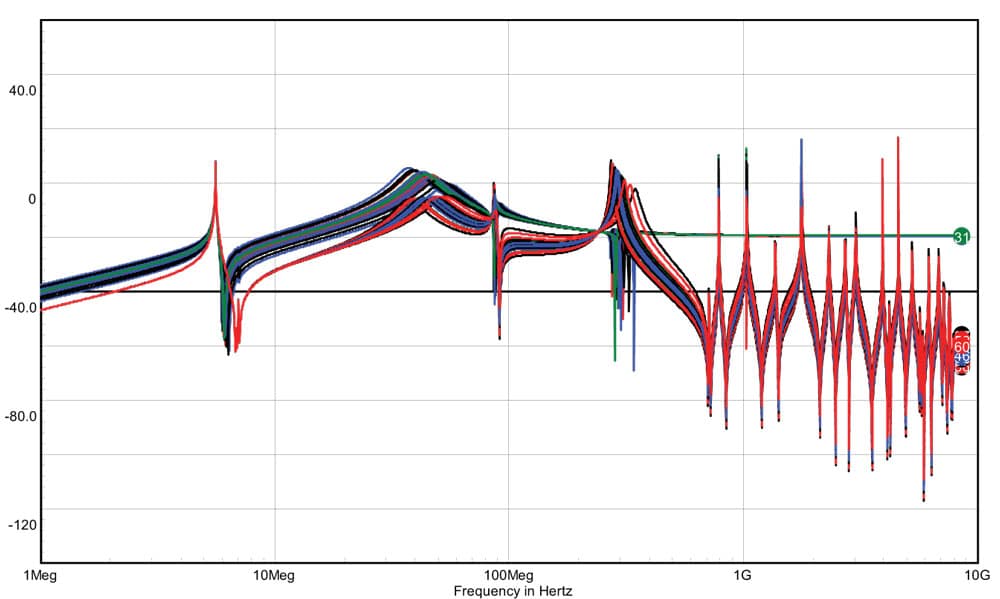

With this conventional decoupling technique, the impedance characteristic on-chip will fluctuate significantly as a result of frequency, the X-Y positioning on the PCB, and the location of other decoupling capacitors (Figure 1). It should be noted that resonances off -chip have little effect on the internal voltage; but at some frequencies, the noise off-chip is greater than that on-chip.

Other techniques for assuring a stable power supply involve the use of an RF-lossy low-pass filter at each supply position to attain current confinement. In effect, each IC supply node is isolated from the rest of the PCB. Th e filtering is achieved using an RF-lossy ferrite bead (e.g., R = 100 Ω @ 100 MHz) as well as the decoupling capacitors mentioned earlier.

ROBUST DECOUPLING

Rather than focusing on the remaining disturbance voltage and the decoupling capacitors found off -chip, it would be prudent to calculate the remaining disturbance voltage on-chip and the resulting ground bounce. The off-chip decoupling current should be kept low and should not include any quality of the resonance frequencies of the decoupling capacitors used in parallel. Lowering the series inductance to enhance recharging will increase the resonance frequency. RF-losses must be provided that will counter the critical supply system resonances. Off -chip RF-lossy inductors will block the instantaneous change of supply current. Also, off-chip buffer capacitance will be needed to maintain the nominal supply voltage within its tolerance, thus allowing the voltage regulators to recoup the necessary voltage level. (cf. EMC-COMPO 2005)

CONCLUSIONS

The IC decoupling schemes typically provided in application notes from various IC suppliers are intended to assure the function of the IC in its application. They do not, however, assure electromagnetic compatibility.

- Leaded packages such as a QFP function as a low-pass filter, but they cause higher RF emissions at higher frequencies (< 100 MHz). See Figure 2.

- BGAs with TLM topology produce a greater level of resonances at higher frequencies (> 100 MHz).

- Creating an isolated power island on the PCB is vital if interference is to be prevented from propagating throughout the PCB.

The decoupling measures taken off -chip have little effect on the on-chip supply bounce, but they can result in a serious escalation of resonances with a typical quality factor of 10 when compared with actual, realistic decoupling component values. Off -chip decoupling, or buff ering, is a necessity, particularly in instances in which the IC has time-variant power consumption and active voltage regulators are used. Off -chip current paths can be confi ned using a Kelvin contact approach (see Interference Technology 2007 Test & Design Guide).

BIBLIOGRAPHY

- Kendall Castor-Perry and Tamar Schmitz, “Prep for Surprises in Modelling a Capacitor Bypass Network, EETimes Europe, Nov 19 and December 9, 2007, pp 34–35.

- E. Engin ( Fraunhofer IZM, Berlin, Germany), M. Coenen, H. Koehne, G. Sommer, and W. John, “Th ree-Pole Analysis Model to Predict SI and EMC Eff ects,” EMC-Compo 2002.

- M. Coenen and R. Derikx, “Vectorial Voltage Measurement for ICs on Multi-IC PWB,” EMC-Compo 2002.

- M.J. Coenen and D. de Greef, “Optimization Techniques for Minimizing IR-drop and Supply Bounce,” EMC-Compo 2005.

- M. Coenen and R. de Jager, “Standardization for EMC IC Modeling” EMC-Compo 2005

- D. de Greef and M. Coenen, “A Pre-Layout IR-Drop Estimator,” EMCCompo 2007.

- M. Coenen and D. de Greef, “Optimal Techniques for Minimizing IR Drop and Supply Bounce,” Interference Technology EMC Test and Design Guide 2007.

- Mart Coenen, “Enhancing Reliability and Reducing Cost by Taking EMC Design Measures First Time Right,” PACE, Eindhoven, the Netherlands, 2007

- Draft IEC 62433-2, Ed. 1: Models of Integrated Circuits for EMI Behavioural Simulation – ICEMCE, ICEM Conducted Emission Model.

- C. Lochot and J.-L. Levant, “ICEM: a new standard for EMC of IC defi nition and examples,” J.L. Levant, 2003 IEEE International Symposium on Electromagnetic Compatibility, August 2003, Vol. 2, pp. 892–897.

- Nobuo Funabiki, Yohei Nomura, Jun Kawashima, Yuichiro Minamisawa, Osami Wada, “A LECCS Model Parameter Optimization Algorithm for EMC Designs of IC/LSI systems,” 17th Annual Zurich Symposium on Electromagnetic Compatibility 2006, 27 February–3 March 2006. pp. 304–307.

- Hideki Osaka, Daisuke Tanaka, Osami Wada, Yoshitaka Toyota, and Ryuji Koga, “Linear Equivalent Circuit and Current Source for I/O (LECCS-I/O) Modeling of IC Power Current for EMI Simulation, and “Linear Equivalent Circuit and Current Source for I/O (LECCS-I/O) Modeling of IC Power Current for EMI Simulation,” JIEP, Vol. 7, No. 6, September 2004, pp. 517–524.

- K. Ichikawa, M. Inagaki, Y. Sakurai, I. Iwase, M.Nagata, and O. Wada, “Simulation of integrated circuit immunity with LECCS model,” 17th Annual Zurich Symposium on Electromagnetic Compatibility 2006, 27 February–3 March 2006. pp. 308–311.

Mart Coenen has over 28 years’ experience in EMC in various fields and has published many papers and publications. He has been actively involved in international EMC standardization since 1988 and last year was awarded with the IEC 1906. He is the former project leader of the standards: IEC 61000-4-6 and IEC 61000-4-2 but has moved his focus towards EMC in integrated circuits. At present, he is convenor of IEC TC47A/WG9 and until last year, a member of WG2.

In addition to his former career with Philips, he is co-founder of the Dutch EMC/ESD Society and part-time lecturer of Post Academic EMC courses. Aside from these activities, he owns a private EMC consulting company.