Lars Glaser

Summary

Physical problems when analyzing an electronic system’s interference immunity.

Introduction

Today it is becoming increasingly difficult to locate faults in state-of-the-art electronic circuits. Apart from a greater complexity (and consequently a much higher number of potential fault sources), small mechanical dimensions make it more and more difficult for the developer to pinpoint faults. Here is an example from measurements.

Task

The control unit of a new disturbance generator for immunity tests was the object of the examination. The circuit board comprises an LCD display (+ controller), µC (142 pin TQFP), FPGA (100 pin TQFP), interface modules, passive components (such as SMD 0603) and various control elements (rotary encoder, push-button, switch). Furthermore, the circuit board hosts USB sockets, connectors for the voltage that will subsequently be generated by the generator and power supply inputs. For cost reasons the circuit board was designed as a two-layer system with feature sizes of 200 µm. There is no continuous GND layer. The busses / lines are laid on both levels. The proximity of the control unit to the generator unit results in high immunity requirements.

Functional faults occurred during the first ESD test according to DIN EN 61000-4-2. After coupling disturbance pulses (contact discharge) into the circuit board’s GND system, the microcontroller crashed which became noticeable by a heartbeat signal failure and frozen display. This fault occurred at different voltages (2.4 kV – 4 kV) depending on the ESD pistol’s position (coupling point and angle). The immunity level clearly had to be raised.

Coupling Mechanism

As shown in [1] there are two potential coupling mechanisms via which disturbances may reach the circuit board’s critical areas: magnetic coupling and electrical coupling.

When using an ESD pistol to couple disturbances into the module, a differentiation has to be made betweenthe two coupling modes.

Figure 1 – Effect of electrical and magnetic fields on the IC

Disturbance currents flow through the circuit board during magnetic coupling and generate magnetic fields which in turn may induce voltages in conductor loops. These voltages may lead to two different types of problems: The induced voltage may either be treated as a logic signal by the circuit’s input or it drives a disturbance current which causes problems in other parts of the control circuit.

Interferences are also caused by electrical coupling. Electric fields capacitively couple into the circuit board’s line networks or components. The resulting displacement current may in turn affect the system in two different ways: the displacement current may cause a voltage drop at a resistor (against Vss or Vdd), which again is recognised as a logic signal, or induce voltages in other parts of the circuit similar to those caused by magnetic coupling.

Disturbances have to be applied to selected individual lines (e.g. in bus systems) and/or their vias or individual IC pins to pinpoint susceptible module components. The aforementioned high level of integration of circuits and feature sizes in the µm range leads to increasing demands on the mechanical resolution of a disturbance source.

Since the functional fault and immunity level were known, a suitable possibility had to be found to increase the system’s interference immunity.

The fault could be narrowed down to the controller in a compliance test. But it still had to be determined which exact pin(s) exactly was/were responsible for the crash. This was absolutely necessary as no appropriate counter-measures (blocking the IC pins, burying the susceptible lines) could otherwise have been effectively taken.

An ESD-like disturbance had to be applied individually to each pin to identify the susceptible lines / IC pins. The ESD pistol could not be used again for several reasons:

– The pulses are too strong for individual IC pins and could easily destroy the circuit.

– The field emitted by the ESD pistol can affect other parts of the circuit and thus significantly hamper specific fault localisation.

– The mechanical dimensions make it nearly impossible to contact an individual pin without short-circuiting the neighbouring pins.

– Due to the line density, there is restricted access to the GND system around the circuit making it difficult to connect the reference line.

Approach

E- or B-field sources are often used to locally inject disturbances. Their selectivity is, however, insufficient in the present case and it did not seem wise to make them even smaller. This would greatly reduce the coupling capacity between the electrode of the E-field source and the respective circuit board structure / component package so that the resulting disturbance pulse is insufficient to reproduce the fault that was noticed before.

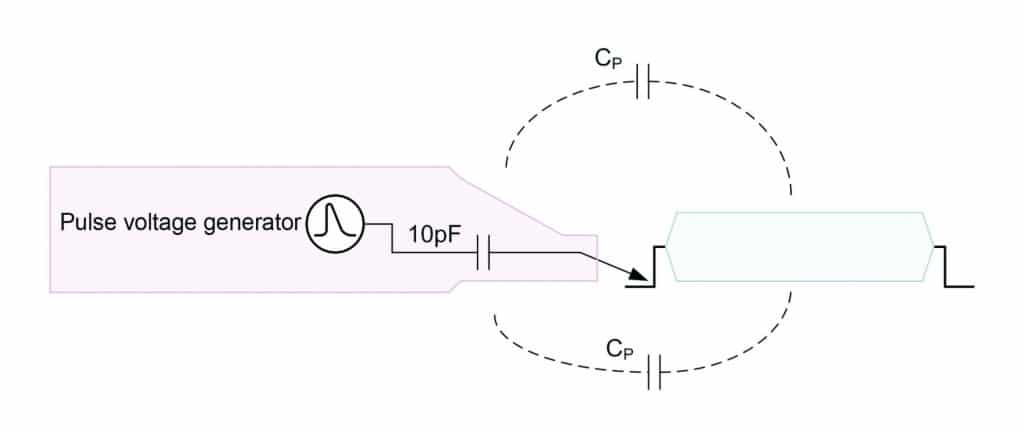

A new disturbance generator was developed to avoid this problem. It generates steep-edged disturbance pulses (1.2 kV / 1.8 ns rise time) which can be coupled into the device under test via an internal capacity (10 pF). The polarity and intensity can be adjusted. A replaceable needle electrode is used to contact a pin, for example.

Figure 2 – Test set-up: pulser (type P23) + IC

This principle offers several advantages:

– The coupling capacity between the structure to which the disturbance has to be applied and the field source is always identical (no longer depending on the distance).

– Individual pins of highly-integrated circuit packages (TQFP) can be contacted separately.

– The coupling capacity versus a small structure is increased.

– Circuits can be tested in the application.

Since no sufficiently short ground connection to the pulse generator is feasible in the immediate vicinity of a real module’s signals to be tested, the generator was designed so that a capacitive coupling to the device under test suffices.

Figure 3 – Pulse shape of the field source at 50 Ω

Figure 4 – Coupling into the IC

The field source’s pulse shape was first examined in a 50 Ω system with a 1 GHz oscilloscope to ensure that the disturbance generated by the pulse voltage source is large enough to interfere with systems. The measurement showed that the 8 V pulse produced by the disturbance generator (type P23) is strong enough to cause an interference with the IC (when applied directly to a pin) despite the capacitive current return path.

Pulse amplitude and curve shape depend on the measurement set-up. For example, the resulting voltage amplitude is higher in case the disturbance is injected into a high-impedance input than into a low-impedance driver output.

A disturbance pulse was applied individually to each IC pin with this measurement set-up. The lowest pulse intensity was initially chosen at a positive polarity. No functional fault could be found during the first test. After gradually increasing the intensity, the same fault pattern as in the compliance test with the ESD pistol appeared. The controller could be made to crash by coupling into two of the 20 lines that lead to the control unit. Only two modifications were initially considered as potential counter-measures: the installation of blocking capacitors against ground and the installation of chip inductances / resistors in the lines between the control unit and controller. After installing two 10 pF 0402 capacitors, P23 was applied to all pins again. The fault did not reappear.

The compliance test with the ESD pistol was then repeated. It became apparent that the faults caused in both tests were interrelated. The immunity level was raised to 4.8 kV.

Conclusion

Disturbances which occur during a device immunity test can be simulated and especially susceptible circuit parts (IC pins / lines) can be identified by local coupling into individual lines or IC pins. It becomes much easier to analyse the cause and the developer can get the bottom of a fault much faster.

Literature

[1] “Neue Aspekte zur ESD-Störfestigkeit“ Elektronik, 05/2009, Author: Gunter Langer

[2] “Neue Burst-Generatoren zur Prüfung der Störfestigkeit von integrierten Schaltungen” 2004, Author: Gunter Langer, Bernd Deutschmann & Günther Auderer